Computer Buses:

According

to computer architecture, a bus is defined as a system that transfers data

between hardware components of a computer or between two separate computers.

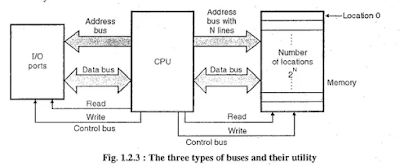

System bus is a single bus that helps all major components of a computer to communicate with each other. It is made up of an address bus, data bus and a control bus.

The

data bus carries the data to be stored, while address bus

carries the location to where it should be stored.

1. Address Bus:

·

Address

bus is a part of the computer system bus that is dedicated for specifying a

physical address.

·

When

the computer processor needs to read or write from or to the memory, it uses

the address bus to specify the physical address of the individual memory block

it needs to access (the actual data is sent along the data bus).

·

More

correctly, when the processor wants to write some data to the memory, it will

assert the write signal, set the write address on the address bus and put the

data on to the data bus.

·

Similarly,

when the processor wants to read some data residing in the memory, it will

assert the read signal and set the read address on the address bus. After

receiving this signal, the memory controller will get the data from the

specific memory block (after checking the address bus to get the read address)

and then it will place the data of the memory block on to the data bus.

·

The

size of the memory that can be addressed by the system determines the width of

the address bus and vice versa. For example, if the width of the address bus is

32 bits, the system can address 2^32 memory blocks (that is equal to 4GB memory

space, given that one block holds 1 byte of data).

2. Data Bus:

·

A

data bus simply carries data. Typically, the same data bus is used for both

read/write operations.

·

When

it is a write operation, the processor will put the data (to be written) on to

the data bus.

·

When

it is the read operation, the memory controller will get the data from the

specific memory block and put it in to the data bus.

·

The

data bus consists of 8, 16, or 32 parallel lines.

·

The

data bus is bidirectional bus, means the data can be transferred from CPU to

main memory and vice versa.

·

The

number of data lines used in the data bus is equal to the size of data word

being written or read.

·

The

data bus also connects the I/O ports and CPU. So, the CPU can write data to or

read it from the memory or I/O ports.

3.

Control Bus:

·

A control bus is part of the system

bus, used by CPUs for communicating with other devices within the

computer.

·

The control bus carries commands from the CPU and returns

status signals from the devices.

·

For example, if the data is being read or written to the

device the appropriate line (read or write) will be active (logic one).

·

The

number and type of lines in a control bus varies but there are basic lines

common to all microprocessors, such as:

- Read (RD): A

single line that when active (logic zero) indicates the device is being

read by the CPU.

- Write (WR): A single line

that when active (logic zero) indicates the device is being written by the

CPU.

- Byte enable (E): A group of lines

that indicate the size of the data (8, 16, 32, 64 bytes).

·

The

RD and WR signals of the control bus control the reading or writing of RAM,

avoiding bus contention on the data bus.

Differences between Address Bus and Data Bus:

|

Sr. No. |

Address Bus |

Data Bus |

|

1 |

It is a computer bus

which is used to specify physical address in memory. |

This bus is used to

transmit data among components. |

|

2 |

It is

unidirectional. |

It is bidirectional. |

|

3 |

Address bus helps to

transfer memory addresses of data and IO. |

Data bus helps to

send and receive data. |

|

4 |

The width determines

amount of memory system can address. |

The width determines

data transfer rates. |

No comments:

Post a Comment